CD4046��ͨ�õ�CMOS�i��h�����·�������c���Դ늉�����������3V��18V����ݔ���迹��(�s100MΩ)���ӑB����С���������l��f0��10kHz�¹��ăH��600μW���������������������Դ늉������������ĵ͡�ݔ���迹�ߵȃ��c���乤���l���_1MHz���Ȳ�VCO �a��50% ռ�ձȵķ�����ݔ���ƽ���cTTL�ƽ��CMOS �ƽ���ݡ�ͬ�r����߀������λ�i����Bָʾ���ܡ�

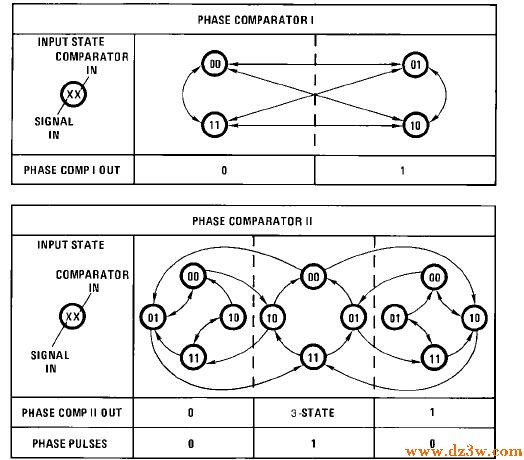

CD4046�Ȳ��Y���D���D��ʾ,���Ѓɂ�PD��VCO�����_�Ŵ�����ݔ����̖�Ŵ��c�����·���Ȳ��������ȡ����������ԭ����ݔ����̖ Ui��14�_ݔ����Ŵ���A1�M�зŴ����κ�ӵ���λ���^�����ݔ��ˣ��D3�_�PK����2�_���t���^����3�_ݔ��ı��^��̖Uo�cݔ����̖Ui����λ���^������λ���^��ݔ�����`��늉�UΨ�t��ӳ�����ߵ���λ�UΨ��R3��R4��C2�V����õ�һ����늉�Ud����������ʎ��VCO��ݔ���9�_���{��VCO����ʎ�l��f2��ʹf2Ѹ�ٱƽ���̖�l��f1��VCO��ݔ���ֽ����������M����λ���^�����^�m�cUi�M����λ���^�����ʹ��f2��f1�����ߵ���λ���һ��ֵ�����F����λ�i�������_�PK����13�_���t��λ���^���������^���c������ͬ������٘����

CD4046�Ȳ��Y���D

�D 1 CD4046�Ȳ��Y���D

CD4046���_�D

�D2 CD4046���_�D

| ��̖

| ���_̖

| �� �Q �� ��

|

| PH11

| 14

| ��λ���^��ݔ��ˣ�������̖ݔ�� ������λ���^��ݔ����̖��ݔ�����S��0.1V���ҵ�С��̖����̖�ڃȲ��Ŵ��ٽ��^�����·��ݔ������λ���^����

|

| PH12

| 3

| ��λ���^��ݔ��ˣ����^��̖ݔ�룩 ͨ��PD����VCO�ą�����̖��

|

| PH01

| 2

| PD��ݔ���� ��λ���^��1ݔ������λ����̖�������î����T�Y�������b�����Ԟ� ��

|

| PH02

| 13

| PD��ݔ���� ��λ���^�����ݔ���ˣ������ã������ؿ���߉��

|

| PH03

| 1

| ݔ���ˣ���λ�}�_ݔ���� ��λ���^��2ݔ������λ����̖���������ؿ���߉���h·���i�r����ƽ���h·ʧ�i�r����ƽ

|

| VC01

| 9

| ������ʎ���Ŀ��ƶˡ�

|

| VC00

| 4

| ������ʎ��ݔ����

|

| INH

| 5

| VCO��ֹ�ˣ�1��Ч ������̖ݔ�룬���ƽ�r��ֹ�����ƽ�r���S������ʎ��������

|

| R1

| 11

| VCO������R1

|

| R2

| 12

| VCO������R2

|

| C1

| 6��7

| ������ʎ���C1���Կ���VCO����ʎ�l�ʡ�

|

| DEM0

| 10

| ���{��̖ݔ����

|

|

| 15

| �Ȳ��������R�{�������O��ؓ�O��

|

CD4046늚Ⅲ��

Absolute Maximum Ratings �^������~��ֵ��

| DC Supply Voltage ֱ�����늉� (VDD)

| −0.5 to +18 VDC

|

| Input Voltageݔ��늉� (VIN)

| −0.5 to VDD +0.5 VDC

|

| Storage Temperature Range����ضȷ��� (TS)

| −65�� to +150��

|

| Power Dissipation���� (PD)

| |

| Dual-In-Line ��ͨ�p�з��b

| 700 mW

|

| Small Outline С���η��b

| 500 mW

|

| ���Ӝض�(TL)������10�룩

| 260��

|

Recommended Operating Conditions ���h�����l����

| DC Supply Voltage ֱ�����늉� (VDD)

| 3 to 15 VDC

|

| Input Voltageݔ��늉� (VIN)

| 0 to VDD VDC

|

| Operating Temperature Range�����ضȷ��� (TA)

| −55�� to +125��

|

DC Electrical Characteristics ֱ��늚����ԣ�

| Symbol ��̖

| Parameter ����

| Conditions �l��

| −55��

| +25��

| +125��

| Units ��λ

| |||||

| ��С

| ���

| ��С

| ����

| ���

| ��С

| ���

| |||||

| IDD

| Quiescent Device Current�o�B���

| Pin5 = VDD, Pin14 = VDD, Pin3,9 = VSS

| |||||||||

| VDD = 5V

|

| 5

|

| 0.005

| 5

|

| 150

| μA

| |||

| VDD = 10V

|

| 10

|

| 0.01

| 10

|

| 300

| ||||

| VDD = 15V

|

| 20

|

| 0.015

| 20

|

| 600

| ||||

| Pin5=VDD, Pin14=Open,Pin3, 9=VSS

| |||||||||||

| VDD = 5V

|

| 45

|

| 5

| 35

|

| 185

| μA

| |||

| VDD = 10V

|

| 450

|

| 20

| 350

|

| 650

| ||||

| VDD = 15V

|

| 1200

|

| 50

| 900

|

| 1500

| ||||

| VOL

| LOW Level Output Voltage ݔ�����ƽ늉�

| VDD = 5V

|

| 0.05

|

| 0

| 0.05

|

| 0.05

| V

| |

| VDD = 10V

|

| 0.05

|

| 0

| 0.05

|

| 0.05

| ||||

| VDD = 15V

|

| 0.05

|

| 0

| 0.05

|

| 0.05

| ||||

| VOH

| HIGH Level Output Voltage ݔ�����ƽ늉�

| VDD = 5V

| 4.95

|

| 4.95

| 5

|

| 4.95

|

| V

| |

| VDD = 10V

| 9.95

|

| 9.95

| 10

|

| 9.95

|

| ||||

| VDD = 15V

| 14.95

|

| 14.95

| 15

|

| 14.95

|

| ||||

| VIL

| ݔ����ƽ늉� ���^������̖

| VDD=5V,VO=0.5V or 4.5V

|

| 1.5

|

| 2.25

| 1.5

|

| 1.5

| V

| |

| VDD = 10V, VO = 1V or 9V

|

| 3.0

|

| 4.5

| 3.0

|

| 3.0

| ||||

| VDD = 15V, VO = 1.5V or 13.5V

|

| 4.0

|

| 6.25

| 4.0

|

| 4.0

| ||||

| VIH

| ݔ����ƽ늉����^������̖

| VDD = 5V, VO = 0.5V or 4.5V

| 3.5

|

| 3.5

| 2.75

|

| 3.5

|

| V

| |

| VDD = 10V, VO = 1V or 9V

| 7.0

|

| 7.0

| 5.5

|

| 7.0

|

| ||||

| VDD = 15V, VO = 1.5V or 13.5V

| 11.0

|

| 11.0

| 8.25

|

| 11.0

|

| ||||

| IOL

| LOW Level Output Current ݔ�����ƽ��� (Note 4)

| VDD=5V, VO = 0.4V

| 0.64

|

| 0.51

| 0.88

|

| 0.36

|

| mA

| |

| VDD=10V, VO = 0.5V

| 1.6

|

| 1.3

| 2.25

|

| 0.9

|

| ||||

| VDD=15V, VO = 1.5V

| 4.2

|

| 3.4

| 8.8

|

| 2.4

|

| ||||

| IOH

| HIGH Level Output Current ݔ�����ƽ���(Note 4)

| VDD=5V, VO = 4.6V

| −0.64

|

| −0.51

| −0.88

|

| −0.36

|

| mA

| |

| VDD=10V,VO = 9.5V

| −1.6

|

| −1.3

| −2.25

|

| −0.9

|

| ||||

| VDD=15V,VO = 13.5V

| −4.2

|

| −3.4

| −8.8

|

| −2.4

|

| ||||

| IIN

| Input Current ݔ�����

| All Inputs Except Signal Input

| |||||||||

| VDD = 15V, VIN =0V

|

| −0.1

|

| −10−5

| −0.1

|

| −1.0

| μA

| |||

| VDD=15V, VIN = 15V

|

| 0.1

|

| 10−5

| 0.1

|

| 1.0

| ||||

| CIN

| Input Capacitance ݔ�����

| Any Input (Note 3)

|

|

|

|

|

|

| 7.5

| pF

| |

| PT

| Total Power Dissipation �����ʺ�ɢ

| fo = 10 kHz, R1 = 1MΩ, R2 =∞, VCOIN = VCC/2

| mW

| ||||||||

| VDD = 5V

|

|

|

| 0.07

|

|

|

| ||||

| VDD = 10V

|

|

|

| 0.6

|

|

|

| ||||

| VDD = 15V

|

|

|

| 2.4

|

|

|

| ||||

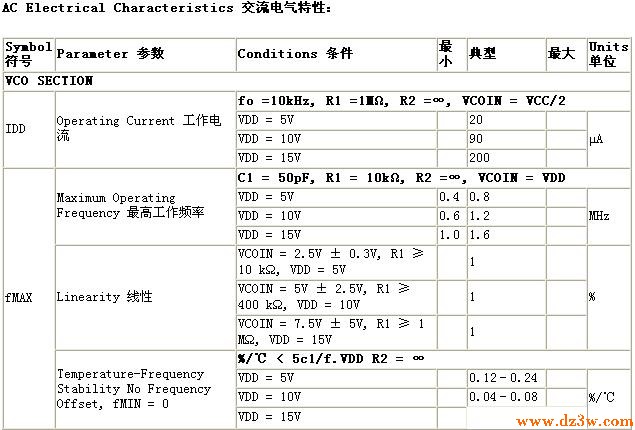

����^��B�D

�D3 CD4046����^��B�D

CD4046���������·�D

�����BCD4046���������·��

�D4 CD4046���͑����·�D

�D4����CD4046��VCO�M�ɵķ����l����������9�_ݔ��˹̶����Դ�r���·�������������ʎ�������á���ʎ���ij䡢������C1����6�_�c7�_֮�g���{�����R1��ֵ�����{����ʎ����ʎ�l�ʣ���ʎ������̖��4�_ݔ�������Dʾ��ֵ����ʎ�l��׃��������20Hz��2kHz��

������d�l��10kHz�M�ɵ��{�l��̖����400Hz���l��̖�{�ƣ������{�l��̖�Ŀ����С��400mV�r����CD4046�r�t�����Ŵ����Ŵ���ý�����ϵ��i��h��14�_ݔ��˭h·����λ���^�����ñ��^���������Ҫ�i��hϵ�y�е������l��f0�����{�l��̖���d�l���@�ӕ�����������ʎ��ݔ���cݔ����̖ݔ���g�a����ͬ����λ��Ķ��ډ�����ʎ��ݔ��ˮa���cݔ����̖�l��׃��������늉�׃�����@��늉�׃����Դ���S�����x���ډ�����ʎ���Ľ��{ݔ����10�_ݔ�����{��̖����VDD��10V��R1��10kΩ��C1��100pF�r���i��h·�IJ�������±0.4kHz�����{��ݔ������ȡ�Q��Դ���S��������R3ֵ�Ĵ�С��

�D5 CD4046�����·�D

�D5��CD4046�cBCD�ӷ�Ӌ����CD4518���ɵ�100���l�·�����_�C�r��f2���ܲ�����f1���ٶ�f2<f1���˕r��λ���^����ݔUΨ����ƽ�����V����Ud��u����ʹVCOݔ���l��f2Ѹ��������f2����ֵ�� f2=f1������˕r Ui���� U0���t��λ���^����ݔ��UΨ����ƽ��UΨ���V����õ���Ud��̖�_ʼ�½����@����ʹVCO��f2�M���{������_��f2/N=f1������f2�cf1����λ��Δφ=0°�����M���i����B������˺�f1�ְl��׃�����i��h���ٴβ��@f1��ʹf2�cf1��λ�i����

![IC�]ُ�W���Ԫ��Ʒ�|����](/static/img/950.jpg)