3λ�딵�ֱ��^оƬICL7107�����Y��

(1) 31/2λ�p�e����A/D�D�Q��ICL7107�����c���c

�� ICL7107��31/2λ�p�e����A/D�D�Q��������CMoS��Ҏģ�����·����������@ʾֵ��ʿ1999����С�ֱ��ʞ�100uV���D�Q���Ȟ�0.05ʿ1 ���֡�

�� ��ֱ���ӹ�ꖘOLED���a�ܣ�����Ҫ������������ʹ���C��·����������ʿ5V�ɽM�Դ��늣�������21�_��GND�ӵ�30�_��IN ��

�� ��оƬ�Ȳ���V+�cCOM֮�g��һ�������Ժܸߵ�2.8V�����Դ��ͨ�^���։����ɫ@������Ļ���늉�VREF ��

�� ��ͨ�^�Ȳ���ģ�M�_�P���F�Ԅ��{����ԄӘO���@ʾ���ܡ�

�� ݔ���迹�ߣ���ݔ����̖�o˥�p���á�

�� ���C�M�b���㣬�o�������Դ������������衢��ݺ�LED��ꖘO���a�ܣ����ܘ���һֱֻ������늉����^��

�� �����ͣ���ƯС���������õĿɿ��ԣ������L��

�� оƬ��������С��15mw��������LED����

�� ���O��һ���T��С���c����̖��ʹ�Õr�Ɍ�LED��ꖘO�����a�ܹ���ꖘO��V+.

�� ���Է�����M�й��ܙz�顣

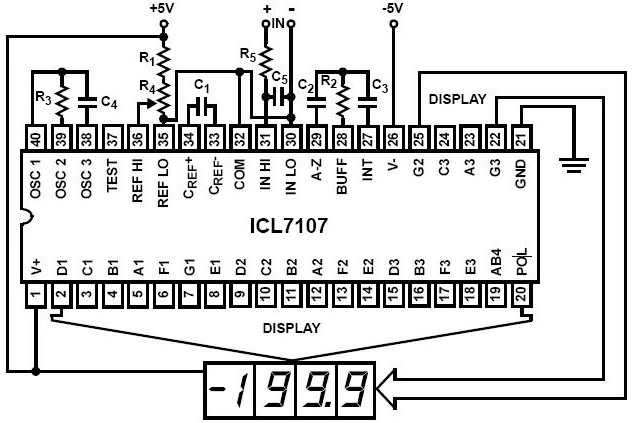

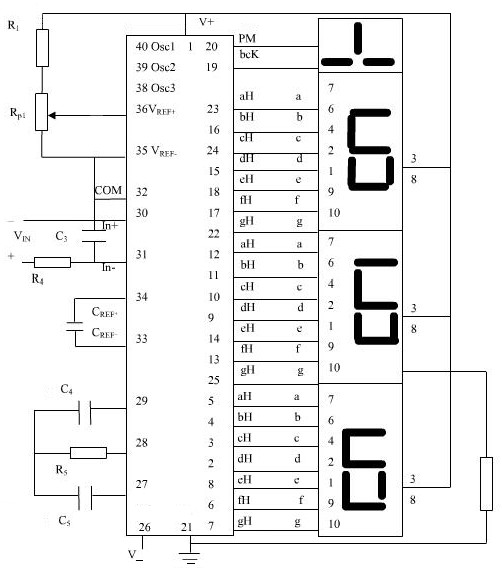

�D1 ICL7107�����_�D�������·��

(2) ICL7107���_���ܼ���Ҫ늚Ⅲ��

V����V-�քe���Դ�����O��ؓ�O��

au-gu,aT-gT,aH-gH���քe�邀λ��ʮλ����λ�P��������̖�����νӂ�λ��ʮλ����λLED�@ʾ���������P��늘O��

Bck��ǧλ�P������̖����ǧλLEO�@ʾ���������ĹP��늘O��

PM��Һ���@ʾ�����湫��늘O���Ӷˣ����Q��늘O��

Oscl-OSc3 ���r���ʎ���������ˣ�������ݻ�ʯӢ���w�M�ɵ���ʎ������38�_����40�_��������x���Ǹ������й�ʽ��Q����

Fosl = 0.45/RC

COM ��ģ�M��̖�����ˣ����Q“ģ�M��”��ʹ �Õrһ���cݔ����̖��ؓ���Լ�����늉���ؓ�O���B��

TEST ���yԇ�ˣ�ԓ�˽��^500�Wķ������߉�·�Ĺ����أ���Ҳ�Q“߉��”��“���ֵ�”��

VREF�� VREF- ������늉���ؓ�ˡ�

CREF����ӻ�����ݶˡ�

INT��27��һ���e�������������x��ض�ϵ��С����ʹ�e������ݔ��늉��a��Ư�ƬF���Ԫ��

IN����IN- ��ģ�M��ݔ��ˣ��քe��ݔ����̖�����˺�ؓ�ˡ�

AZ���e�����ͱ��^���ķ���ݔ��ˣ����Ԅ��{�����CAz �����������200mV�M�̶ȵĈ�����ʹ��0.47μF����2V�M�̶���0.047μF��

BUF�����_�Ŵ���ݔ���ˣ��ӷe�����Rint����ݔ�����ğo�����( idling current )��100μA�������_���c�e�����܉o20μA����������Ĵ��_��һ��Rint���e�����������ֵ�ڝM�̶�200mV�r�x��47K����2V�M�̶Ȅtʹ��470K��

ICL7107��Ҫ������

�Դ늉�

| ICL7107 V+ to GND

| 6V

| �ضȷ���

| 0�� to 70��

| ||

ICL7107 V- to GND

| -9V

| �����

| PDIP���b

| qJA(��/W)

| 50

| |

MQFP���b

| 80

| |||||

ģ�Mݔ��늉�

|

| V+ to V-

| ���Y��

| 150��

| ||

����ݔ��늉�

|

| V+ to V-

| ��߃���ضȷ���

| -65�� to 150��

| ||

�r�ݔ��

|

| GND to V+

|

| |||

����ʎ����Tc=2RCIn1.5=2.2RC ��

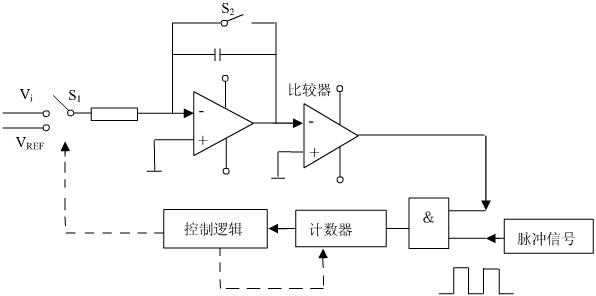

�D2 ICL7107A/D�D�Q��ԭ��

Ӌ����������e���^�̵ĕr��}�_�M��Ӌ��������߉�������l�����g�a������λ���������������i������

���l���Á팦�r��}�_��u���l���õ������Ӌ���}�_fc��ꖘOLED���a�ܹ���늘O����ķ�����̖fc��

�g�a����BCD-7���g�a������Ӌ������BCD�a�g��LED���a���߶ιP���M�ɔ��ֵ��������a��

�����nj��g�a��ݔ�������ڹ�ꖘO���a���߶ιP����߉�ƽ׃���������P���ķ�����

����������������������һ���R�e�e�����Ĺ�����B���m�r�l��������̖��ʹ��ģ�M�_�P��ͨ����_��A/D�D�Q����ѭ�h�M�С��ڶ����R�eݔ��늉��O�ԣ�����LED���a�ܵ�̖ؓ�@ʾ���ڶ�����ݔ��늉������ޕr�l�������̖��ʹǧλ�@ʾ“1" ������aȫ��Ϩ�硣

��i�����Á����A/D�D�Q�ĽY�����i������ݔ�����g�a������LED ������ÿ���y�������Ԅ��{�㣨AZ������̖�e�֣�INT���ͷ���e�֣�DE�������A�Ρ�

��һ�A�Σ��Ԅ��{���A��AZ

�D�Q�_ʼǰ���D�Q������̖VL=0) ���Ȍ�Ӌ�r�����㣬����ͨ�_�PS0 ��ʹ�e�����C��ȫ��늡�

�ڶ��A�Σ���̖�e��INT

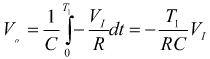

���_�PS1�ϵ�ݔ����̖V1һ�ȣ��e������V1�M�й̶��r�gTl�ķe�֣��e�ֽY���飺

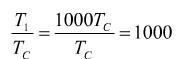

��ʽ�f������Tl�̶��l����V0�cVl�����ȡ�

�����A������e��DE

���_�PS1�D������늉�VREFһ�ȣ��e��������e�֡�����e������ݔ��늉�����������r�������^�ķe�֕r�gT2�t�ɵã�

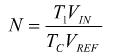

�ʿɵõ���

��Ҋ������e�ֵ�V0=0�@�Εr�gT2�cVl�����ȡ���r��}�_CD�����ڞ�Tc��Ӌ��������T2�r�g��Ӌ��ֵ��N�ã�T2=NTc

������ʽ�ã�

������֪��T1,Tc��VREF�̶���׃��Ӌ��ֵN�H�cVIN�����ȣ����F��ģ�M�������������D׃��

�����BA/D�D���^�̵ĕr�g���䡣���O�r��}�_�l�ʞ�40KHz��ÿ�����ڞ�4000Tc,

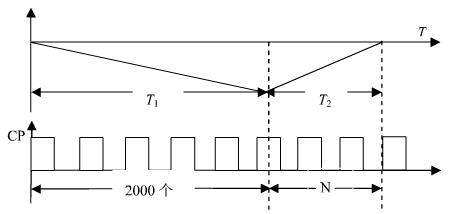

��D3��ʾ��ÿ���y�������������A�ι����Ԅ�ѭ�h��

�D3 �p�e����A/D�D�Q����늉����ΈD

���A�Εr�g��������

����̖�e�֕r�gTl��1000Tc ��

����̖����e�֕r�gT2��0һ2000Tc ���@�Εr�g���L������VIN�Ĵ�С�Q���ġ�

���Ԅ��{��r�gT0��1000��3000Tc ��

������ķ�����֪��Tl �̶���׃�ģ���T2�SVIN�Ĵ�С����׃����飬

�x����늉�VRFF = 100.0mv ,

�ɣ� �ã�VIN=0.1N

�ã�VIN=0.1N

�M���̕rN=2000��ͬ������ʽ�Ɍ����M���̕rVIN�c����늉����Pϵ�飺VIN=2VREF ��������߃x���Ŀ��ɔ_������ͨ���x���IJɘӕr�gTl �鹤�l���ڵ����������҇�����50Hz����늾W�������ڞ�20ms�����xT1=n×20ms��n= l,2,3……nԽ����ģ�ɔ_����������Խ������nԽ��A/D�D�Q�ĕr�gԽ�L����ˣ�һ��ȡTl=100ms����f0��40KHz ��

��T0=2RC105=2.2RC����

ʽ��T0����ʎ���ڡ�

����ʽ��֪����f0=40KHz�r������Ԫ�����xȡ����Ψһ��ֻҪ�M��Ҫ�ɡ�

�D4 ICL7107�cLED�Ӿ��·�D

(3) ICL7107�Ĺ���ԭ��

�p�e����A/D�D�Q��ICL7107��һ�N�g��A/D�D�Q������ͨ�^��ݔ��ģ�M늉��ͅ���늉��քe�M�Ѓɴηe�֣���ݔ��늉�ƽ��ֵ׃�Q���c֮�����ȵĕr�g�g����Ȼ�������}�_�r�g�g�����M���ó������Ĕ�����ݔ����

����ԭ���Կ�D��D2��ʾ���������e���������^����Ӌ����������߉�͕r���̖Դ���e������A/D�D�Q�������K����һ���y�����ڃȣ��e�����Ⱥ�ݔ����̖늉��ͻ���늉��M�Ѓɴηe�֡����^�����e������ݔ����̖�c���ƽ�M�б��^�����^�ĽY�����锵���·�Ŀ�����һ̖���r���̖Դ�Ę˜�����Tc����y���r�g�g���Ę˜ʕr�g�������ɃȲ��ăɂ��������Լ��ⲿ��RC�M�ɵġ�

![IC�]ُ�W���Ԫ��Ʒ�|����](/static/img/950.jpg)